Hamming code is useful in Error Correction in Linear Block Code. This code will encode four bits of data and generate seven bits of code by adding three bits as parity bits. It was introduced by Richard W. Hamming. This algorithm can detect one and two bit error and can correct one bit error. Given below code will generate (7,4) Systematic Hamming Encoder. This encoder will use Least Significant 4 bits as data inputs and Most 3 significant bits as a parity bits.

Get VHDL Code.

1 2 3 4 5 6 7 8 9 10 11 12 13 | module hamming_ecoder( input [3:0] data_in, output [6:0] ham_out ); wire p0,p1,p2; assign p0 = data_in[0] ^ data_in[1] ^ data_in[3]; assign p1 = data_in[0] ^ data_in[2] ^ data_in[3]; assign p2 = data_in[1] ^ data_in[2] ^ data_in[3]; assign ham_out = {data_in, p0, p1, p2}; endmodule |

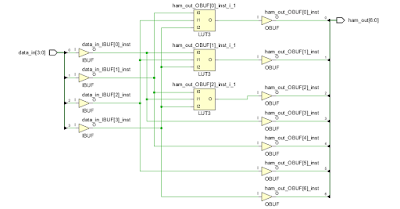

RTL view of above code is shown below. Above code is synthesized by Xilinx Vivado tool.

Testbench for above design code is given below.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 | `timescale 1ns / 1ps module hamming_encoder_tb(); reg [3:0] data_in; wire [6:0] ham_out; hamming_encoder DUT(data_in,ham_out); initial begin data_in = 4'h4; #10; data_in = 4'h0; #10; data_in = 4'h8; #10; data_in = 4'hF; #10; data_in = 4'hA; #10; data_in = 4'h9; #10; end endmodule |

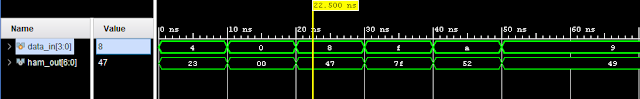

Above testbech code is simulated and waveform result is shown below.

No comments:

Post a Comment