In VHDL, delays are specified only in signal assignment not in variable assignment. Delays are not synthesizable. There are two types of delay in VHDL Language.

- Transport Delay

- Inertial Delay

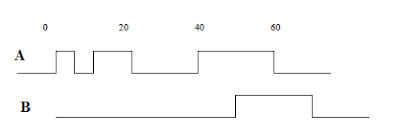

- Transport Delay : It is the delay model just delay the signal or change the value of the signal by the time specified in the after clause. It is the characteristic of the hardware elements that exhibits infinite frequency response. Any pulse is transmitted no matter how small it is.

- Example : B <= transport A after 10 ns;

- Inertial Delay : It is used to model switching circuits. This delay is the default delay. Any pulse whose duration is less than of the switching time of the circuit is not passed. To reject a pulse of predefined width, VHDL can model devices by adding a "reject" clause to the assignment statement.

- Example : B <= inertial A after 10 ns;

- It will reject pulse whose width is less than 10 ns and passes pulse with greater than 10 ns.

|

| Transport Delay |

|

| Inertial Delay |

No comments:

Post a Comment